Sicherheitslücken in der Hardware durch eine zuverlässige Abbildung des Chip-Layouts erkennen

In vielen Gegenständen des Alltags wie dem Smartphone, der Haussteuerung oder dem Auto, aber auch in industriellen Anlagen oder medizinischen Geräten befinden sich Chips – nur wenige Quadratmillimeter kleine Halbleiterplättchen, auf denen äußerst komplexe Schaltungen mit mehreren Milliarden Bauelementen untergebracht sind.

Versierte Angreifer können diese Halbleiterchips verändern, sodass die darauf laufenden kryptografischen Verfahren ausgehebelt oder sensible Daten ausgelesen werden können. Ebenso können Angreifer über korrumpierte Chips Funktionen umprogrammieren oder Geräte vollständig kontrollieren.

Die einzelnen Fertigungsschritte in der Herstellung von Chips bieten einem Angreifer vielfältige Möglichkeiten, gezielte Veränderungen vorzunehmen. Daraus ergibt sich die Notwendigkeit, fertig integrierte Schaltungen nicht nur in ihrer Funktion, sondern auch in ihrem Layout zu verifizieren.

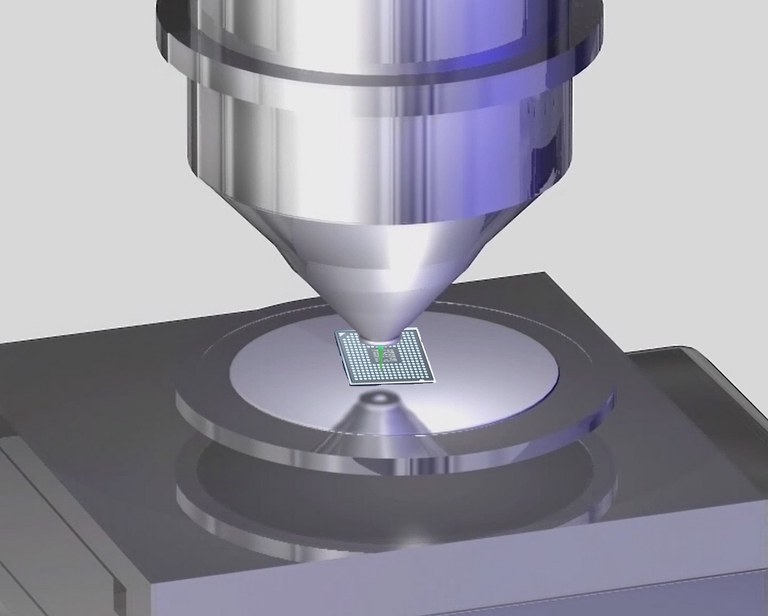

Ziel des Verbundprojektes SyPASS ist die Erforschung einer effizienten fehlerfreien Abbildung des Layouts integrierter Schaltungen mit Strukturen, die 40 nm breit oder noch kleiner sind. Zum Vergleich: Ein menschliches Haar hat einen Durchmesser von ca. 50.000 nm.

Im Projekt werden Lösungen zum Freilegen sowie zum präzisen, rasterelektronenmikroskopischen Abbilden von Chipstrukturen entwickelt. Aus den Bildern werden Mosaikbilder einzelner Ebenen erzeugt und daraus über mehrere Ebenen zueinander justierte Layouts rekonstruiert. Dabei werden Abbildungsfehler automatisch erkannt und zuverlässig korrigiert.

Die Leistungsfähigkeit der Verfahren wird anhand speziell konzipierter Testmuster evaluiert. Die auf diese Weise gewonnene hohe Qualität der Daten erlaubt eine zuverlässige dreidimensionale Modellbildung des Layouts.

Die Verfügbarkeit des Layouts integrierter Schaltungen bildet die Basis für darauf aufbauende Analysen – z. B. zur Erkennung von Manipulationen, zur Erhöhung der Qualität oder der Sicherung von Schutzrechten.

Durch die weiter zunehmende Vernetzung in Anwendungen wie Industrie 4.0, Energieversorgung und Mobilität sowie durch die steigende Verbreitung mobiler Geräte wird der Bedarf an vertrauenswürdigen Chips weiter wachsen.

Für neueste Chipgenerationen reichen die derzeitigen Technologien für eine erfolgreiche Gewinnung des Layouts nicht mehr aus. Im Projekt werden daher neue Lösungsansätze für Verfahren bis hin zu Systemen für die effiziente Präparation, die Abbildung und Synthese von Bildern mit dem Ziel der Verifikation des Layouts entwickelt – auch für künftige Chipgenerationen.